����ʱ�䣺�������ࣺ�����ְ�����������1��

ժ Ҫ�� ժ Ҫ��Ϊ���о� H D B3 ��ı���ԭ�������������ַ�����ʵ�� H D B3 �������������һ���Ƚ��з� 0 ��ļ��Ա仯�������ԵIJ� V ������Ȼ���ٽ��д����Բ� B ����;���������Ƚ��в� V �������ٽ��в� B ����������ٽ��м��Ա仯�������֤�ɵã���ʱ��Ƶ��Ϊ 100 M H

����ժ Ҫ��Ϊ���о� H D B3 ��ı���ԭ�������������ַ�����ʵ�� H D B3 �������������һ���Ƚ��з� 0 ��ļ��Ա仯�������ԵIJ� V ������Ȼ���ٽ��д����Բ� B ����;���������Ƚ��в� V �������ٽ��в� B ����������ٽ��м��Ա仯�������֤�ɵã���ʱ��Ƶ��Ϊ 100 M H zʱ����Ȼ���ַ�������ʵ�� H D B3 ��ı��룬���ҹ�����ͬ���������ַ���Ӳ����·��ռ�õ�������Ԫ����ͬ��������ռ�õ�������Ԫ�ȷ���һ�� 9 ������ˣ��ڹ���һ��������£����������ڷ���һ��

�����ؼ��ʣ�FPG A ;H D B3 ��;����Դ;����

����Ϊ����Ӧ�ŵ����ź��ڴ���ǰһ��Ҫ���б��봦��[1]��������ʽ���ֶ������� H D B3 ���Ƶ�ɷ��٣������� 0 ������ 3 ����������ֱ�����ԣ�����Ӧ�÷�Χ�Ϲ�[2]�����о����� V H D L ���ԣ���������� H D B3 ������������������ֱ���ϵͳ�����˶Աȷ���[3]��

����1�������ԭ��

����H D B3 ����Ҫ�� 3 ���ؼ������ã����м��Ա仯�����в� V ���������в� B ����[4]��

�������м��Ա仯������ 0 ��ʱ�����伫�����������仯[5 6]��

�������в� V �������������������� 4 �� 0�����ڸô����� V ���������ԭ�������

�������в� B �������ж������������������� V ����֮��ķ� 0 ������������ֵΪż������ô�㽫 B ����������ж�Ӧ��λ�ã�����ͱ���ԭ�������

����������У����ַ����� 3 ���ؼ�����ִ��˳��һ��������һ���ȶ����н��з� 0 �뼫�Ա仯�������Բ� V ������Ȼ���ٶ����н��д����Բ� B ����;���������Ƚ��в� V ������Ȼ���ٽ��в� B ����������ٽ��м��Ա仯��

����2�����Ӳ����·

����2.1 ����һ��Ӳ����·

����chaV �Ƿ� 0 �뼫���γɼ������Բ� V ģ�飬�ڴ�Ӳ����·�У��ù���ģ���� flag_v_1�vflag_v_v�w����ǰ һ���� 0 ��vǰһ V ��w�ļ��ԣ�����־�ź�Ϊ 0 ���������Ϊ������Ϊ 1 ��Ϊ��[7]���������ź� inputΪ 1 ʱ������ flag_v_1 ��ֵ��out_v �����Ӧ�ļ����ź�[8];�������ź� inputΪ 0 ʱ����ô���ü������ͽ��м�һ���������ͬʱ�жϸü�������ֵ�Ƿ���� 4������պõ��� 4����ô out_v �˿ڱ����һ�� V�v�� V ����������ǰһ���� 0 ���ű�����ͬ������ V �ķ��������仯�w������ԭ�����[9]��

����chaB �Ǵ����ԵIJ� B ģ�飬�ڴ�Ӳ����·�У��ù���ģ�������λ��λ�Ĵ��������д����Բ� B �������� chaV ģ�������ź� out_v ������λ�Ĵ���ʱ��chaB ģ���е���λ�Ĵ����ĵ��ļ�ͬʱ�жϸ������ź��Ƿ�Ϊ V�v+ V �� V�w������ǣ�������жϵ�ǰ V �ļ����Ƿ��ǰһ���� 0 �뼫����ͬ�������ͬ����ô out_b ��ԭ��������������ͬ����ô out_b ������뵱ǰ V ������ͬ�� B�v���ڲ�������λ�Ĵ�����ʹ���������� B ������ V ��֮���һ���� 0 ���ź�w��

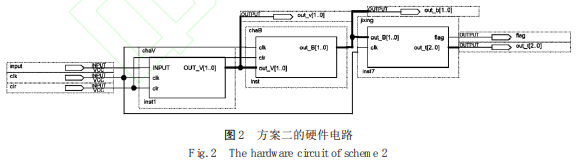

����2.2 ��������Ӳ����·

������������Ӳ����·��ͼ 2 ��ʾ��chaV ��chaB��jixing �ֱ��Dz� V ģ�顢�� B ģ��ͼ����γ�ģ�顣

�����ڴ�Ӳ����·�У�chaV ģ�����ж������ź� input�Ƿ�Ϊ 0�����ǣ�������ж��Ƿ�Ϊ�� 4 �� 0�����ǣ��� out_v ��� V�v�������ԩw���������ԭ�������chaB ģ�������λ��λ�Ĵ��������в������Բ� B �������� chaV ģ��������ź� out_v ������λ�Ĵ���ʱ��chaB ģ���е���λ�Ĵ����ĵ� 4 ��ͬʱ�жϸ������ź��Ƿ�Ϊ V ������ V ����ʼ������ 0 ��ĸ�����ֱ����һ�� V ����������ͬʱ�жϸü���ֵ����ż�ԣ���Ϊż��������� B�v���� chaB ģ���������λ�Ĵ�����ʹ����������� B �� 2 �� V ���к�һ�� 0 ���ź�w������ԭ�������

������ out_b �źŽ��� jixing ģ��ʱ����ģ����� flag �źũvǰһ�� 0 ���� B �ļ��Ա�־�w�� 0 �� B �����������Խ��棬ͬʱҲ�ɵõ� V �ļ��ԣ������ H D B3 �� out_t��

����3��������������

����3.1 ����һ�ķ����������

�����ڴ˷����У�input������Ĵ������źţ�clk Ϊ 100 M H zʱ�Ӷˣ�clr������ˣ�flag_v_1��flag_v_v �ֱ���ǰһ�� 0 �롢ǰһ V ��ļ��Ա�־���ɷ���ɵã������� 10011000011100001100001011 ʱ���� V �����������γ��ź� out_v �� + 100 1 + 1000 + V 1 + 1 1000 V + 1 1000 + V 10 + 1 1�v����� 0 ���� 0��1 ���� B��2 �� �� 1��3 �� �� V ��5 �� �� + B��6 �� �� + 1��7 �� �� + V ���� ô �� Ӧ �� ʮ �� �� Ϊ 60026000726200036200072062�w���� B ����źũvH D B3 ������źũwout_b �� + 100 1 + 1000 + V 1 + 11000 V + 1 1 + B00 + V 1 + 1 1�v��Ӧ��ʮ����Ϊ 60026000726200036250072062�w��������ʹ������λ�Ĵ���������������ӳ�[10]��

��������һ�Ĺ�����ͼ 4 ��ʾ���ܹ���Ϊ 63.86 m W ����̬����Ϊ 60.15 m W ��I/O ����Ϊ 3.71 m W ��

��������һ����Դռ����ͼ 5 ��ʾ�������ռ�� 57 ��������Ԫ��ռ�� 69 ����

����3.2 �������ķ����������

�����������ķ�������ͼ 6 ��ʾ

����10011000V 111000V 11000V 1011�v���� 0 �� �� 0��1 �� �� 1��2 �� �� B��3 �� �� V ���� ô �� Ӧ �� ʮ �� �� Ϊ 10011000311100031100031011�w���� B ��������ź� out_b �� 0011000V 111000V 11B00V 1011�v0 ���� 0��1 ���� 1��2 ���� B��3 ���� V ����ô��Ӧ��ʮ����Ϊ 10011000311100031120031011 �w������ת������źũvH D B3 ������źũwout_t�� + 100 1 + 1000 + V 1 + 1 1000 V + 1 1 + B00 + V 10 + 1 1�v0 ���� 0��1 ���� B��2 �� �� 1��3 �� �� V ��5 �� �� + B��6 �� �� + 1��7 �� �� + V ���� ô �� Ӧ �� ʮ �� �� Ϊ 60026000726200036250072062�w��������ʹ������λ�Ĵ���������������ӳ١�

�����������Ĺ�����ͼ 7 ��ʾ���ܹ���Ϊ 63.86 m W ����̬����Ϊ 60.15 m W ��I/O ����Ϊ 3.71 m W ��

����4���Աȷ���

����������У����ַ����� 3 ���ؼ�����ִ��˳��һ��������һ���Ƚ��з� 0 �뼫�Ա仯�������Բ� V ������Ȼ���ٽ��д����Բ� B ����;���������Ƚ��в� V ������Ȼ����в� B ����������ٽ��м��Ա仯����Ȼ�������ַ������ܶ������źŽ��� H D B3 ����룬���ҹ�����ͬ������ռ�õ�����Դ��ͬ�����ܱȽ���� 1 ��ʾ��

�����ӱ� 1 ���Կ������ڹ�����ͬ������£�������ռ�õ�������Ԫ�ȷ���һ�� 9 �������������˵���������ڷ���һ����������ƿ��ܲ������ŵģ�����������������ں����Ĺ�������Ҫ�����Ż������ַ�����——�������ߣ��� �N��Ф˳��

�����ο����ף�

����[1] �μ���������ΰ.����ͨ��ϵͳ��ģ�����[M ].���������ӹ�ҵ�����磬2004��1 288.

����[2] �����ţ��Ÿ���ɿ�.ͨ��ԭ��[M ].5 ��.������������ҵ�����磬2001��77 78.

����[3] ���.���� FPG A �� LD PC ���������о�[D ].���ţ����ȴ�ѧ��2018.

����[4] ������.���� CPLD �� H D B3 �������·�����[J].�������Ϣ��2010��26�v2�w��169 171.

����[5] л����.���� SO PC ������ H D B3 ���������[D ].������������ѧ��2014.

����[6] ���.���� System V iew �� H D B3 ���������[J].��Ϣͨ�ţ�2014�v9�w��41.

����[7] ��־ǿ�����˱�����.���� FPG A �� H D B3 ����뷽�����������е絼̽�������⾮�е�Ӧ��[J].ʯ�������� 2012��26�v2�w��76 79.

����[8] �̱�.�����ܶ�˫���� H D B3 ������� V H D L ��Ƽ�����[D ].���ݣ����ݴ�ѧ��2008.

����[9] �����ϣ�����̩.���� FPG A �� H D B3 ��������Ż���������[J].�ִ����Ӽ�����2011��34�v24�w��146 148.

����[10] ���ɣ��Ƽ�ҵ.ED A ʵ�ý̳�[M ].��������ѧ�����磬2005��77 79.